## Agilent E2920 PCI-X Series Opt. 320 C-API/PPR

## **Programming Guide**

Agilent Technologies

#### **Important Notice**

All information in this document is valid for Agilent E2929A, Agilent E2929B, Agilent E2922A and Agilent E2922B testcards.

© Agilent Technologies, Inc. 2002

#### Revision

June 2002

Printed in Germany

Agilent Technologies Herrenberger Straße 130 D-71034 Böblingen Germany Authors: t3 medien GmbH

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data

#### **Safety Notices**

CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### Trademarks

Windows NT <sup>®</sup> and MS Windows <sup>®</sup> are U.S. registered trademarks of Microsoft Corporation.

## Contents

| About This Guide |                                                                                           | 7        |

|------------------|-------------------------------------------------------------------------------------------|----------|

| Documentation O  | verview                                                                                   | 9        |

| Programming Ove  | erview                                                                                    | 11       |

|                  | Programming Interfaces                                                                    | 12       |

|                  | C Programming Libraries                                                                   | 13       |

|                  | Generic C-API Functionality                                                               | 14       |

|                  | Protocol Permutation and Randomization Functionality                                      | / 15     |

|                  | Exception Handling                                                                        | 15       |

|                  | Getting Started                                                                           | 17       |

|                  | How to Get Started                                                                        | 18       |

|                  | Example for Getting Started                                                               | 20       |

|                  | Benefits                                                                                  | 21       |

| Programming the  | Exerciser                                                                                 | 23       |

|                  | Reading From and Writing To the Memories                                                  | 26       |

|                  | Downloading Settings and Running the Exerciser                                            | 27       |

|                  | Programming the Exerciser as a Requester-Initiator                                        |          |

|                  | Device                                                                                    | 28       |

|                  | Programming Generic Requester-Initiator Properties                                        | 29       |

|                  | Programming Requester-Initiator Block Transfers                                           | 30       |

|                  | Programming the Behavior of Block Transfers                                               | 35       |

|                  | Programming the Exerciser as a Completer-Target Dev                                       | ice      |

|                  | 40                                                                                        |          |

|                  | Programming a Target Decoder                                                              | 41       |

|                  | Programming the Configuration Space                                                       | 45       |

|                  | Programming the Completer-Target Behavior Programming Conoria Completer Target Properties | 48       |

|                  | Programming Generic Completer-Target Properties<br>Programming a Split Condition          | 52<br>53 |

|                  | r rogramming a Spirt Condition                                                            | 55       |

| Programming the Exerciser as a Completer-Initiator |       |

|----------------------------------------------------|-------|

| Device                                             | 55    |

| Programming Generic Completer-Initiator Properties | 55    |

| Programming the Completer-Initiator Behavior       | 57    |

| Programming the Exerciser as a Requester-Target D  | evice |

| 61                                                 |       |

| Programming Generic Requester-Target Properties    | 61    |

| Programming a Split Completion Decoder             | 63    |

| Programming the Requester-Target Behavior          | 63    |

| Controlling the Exerciser                          | 67    |

| Scheduling Block Transfers and Split Completions   | 68    |

| Programming the Data Generator                     | 73    |

| Programming Errors Injection                       | 76    |

| Programming the Expansion ROM                      | 80    |

| Programming the Data Memory                        | 81    |

| How to Program the Data Memory                     | 83    |

| Example for Programming the Data Memory            | 83    |

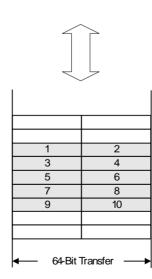

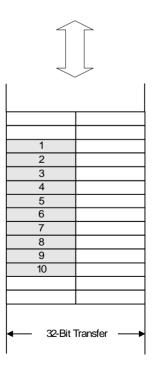

| Programming Data Transfer To and From the Host     | 84    |

| Example for Host Access                            | 84    |

| Programming PCI-X Interrupts                       | 85    |

| How to Generate PCI-X Interrupts                   | 85    |

| Example for Programming PCI-X Interrupts           | 87    |

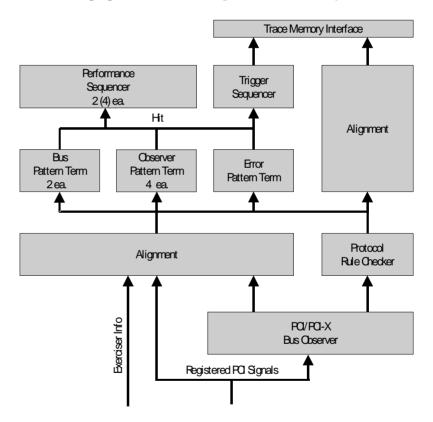

| Programming the Analyzer                           | 89    |

| Programming the Protocol Observer                  | 90    |

| How to Program the Protocol Observer               | 91    |

| Example for Programming the Protocol Observer      | 93    |

| Programming Pattern Terms                          | 94    |

| How to Program Pattern Terms                       | 94    |

| Example for Programming Pattern Terms              | 95    |

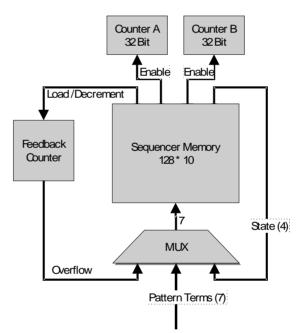

| Programming the Trigger Sequencer                  | 96    |

| How to Program the Trigger Sequencer               | 99    |

| Example for Programming the Trigger Sequencer      | 100   |

| Programming the Trace Memory                       | 104   |

| How to Program the Trace Memory                    | 105   |

| Example for Programming the Trace Memory           | 106   |

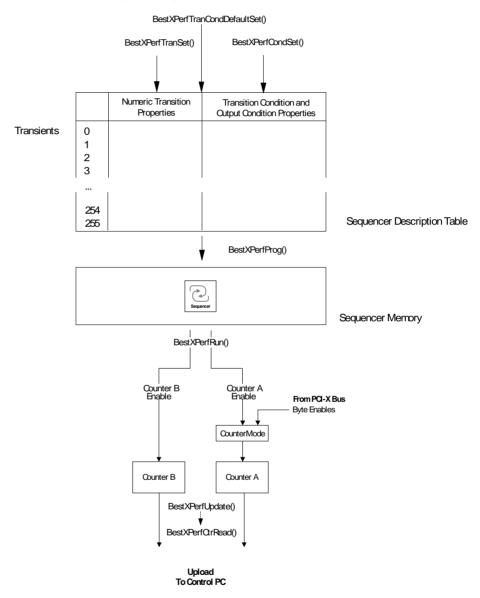

| Programming the Performance Sequencer             | 111 |

|---------------------------------------------------|-----|

| How to Program the Performance Sequencer          | 113 |

| Example for Programming the Performance Sequencer | 115 |

### **Programming Protocol Permutator and Randomizer Properties**

117

| Introduction                                       | 118 |

|----------------------------------------------------|-----|

| Contributions of the PCI-X PPR Software            | 120 |

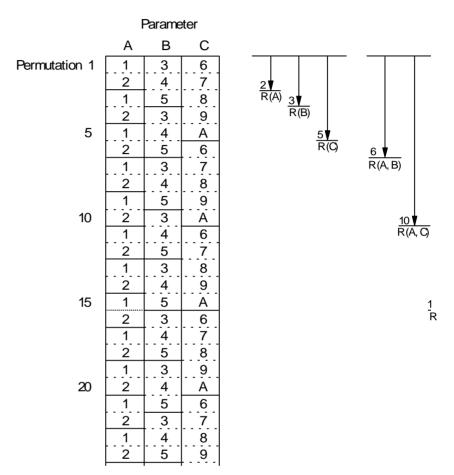

| Operation Principles                               | 121 |

| Generating Permutations                            | 123 |

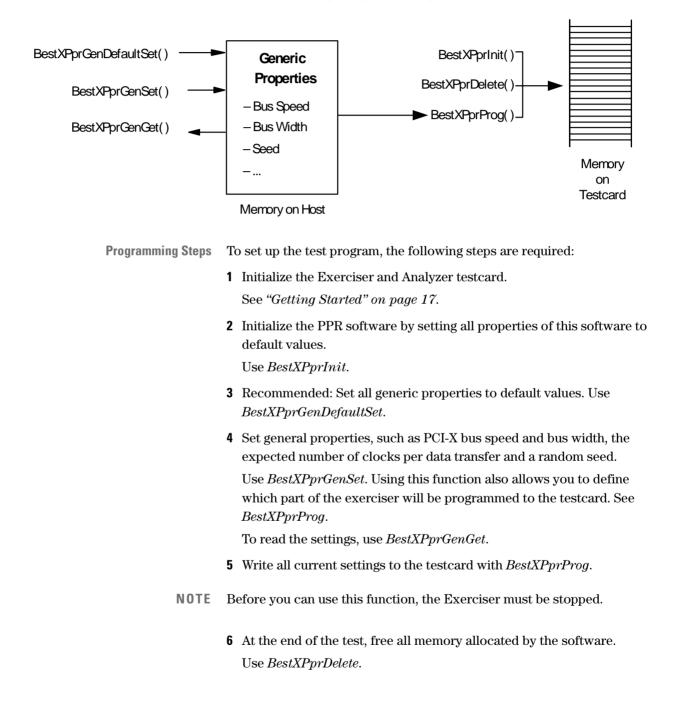

| How to Write a Test Program                        | 127 |

| Example Test Design                                | 128 |

| Preparing for PPR Programming                      | 131 |

| How to Prepare for PPR Programming                 | 132 |

| Example for Preparing for PPR Programming          | 133 |

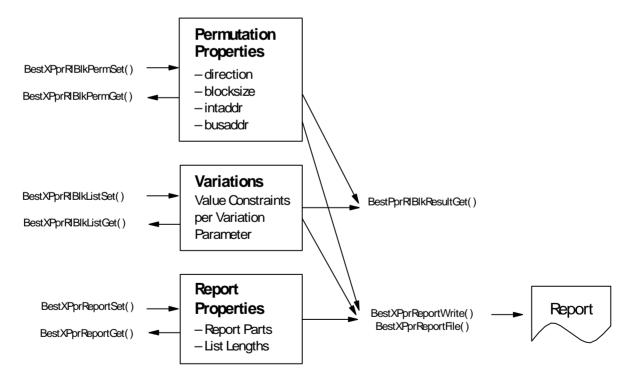

| Programming Requester-Initiator Block Permutations | 134 |

| How to Program RI Block Permutations               | 139 |

| Example for Programming RI Block Permutations      | 141 |

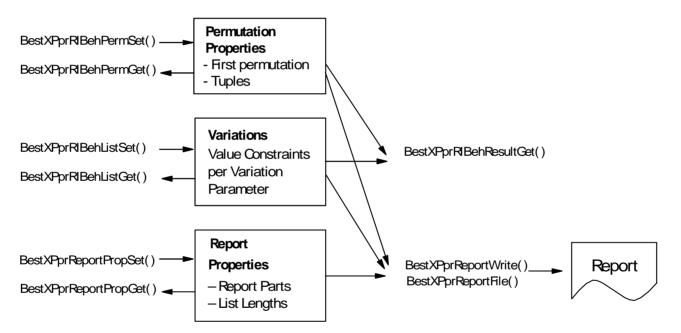

| Programming RI Behavior Permutations               | 142 |

| How to Program RI Behavior Permutations            | 144 |

| Example for Programming RI Behavior Permutations   | 146 |

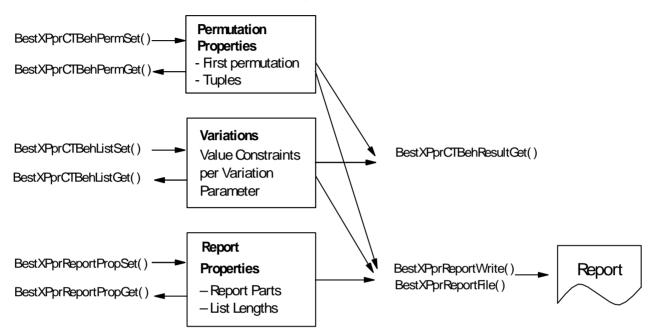

| Programming CT Behavior Permutations               | 147 |

| How to Program CT Behavior Permutations            | 148 |

| Example for Programming CT Behavior Permutations   | 149 |

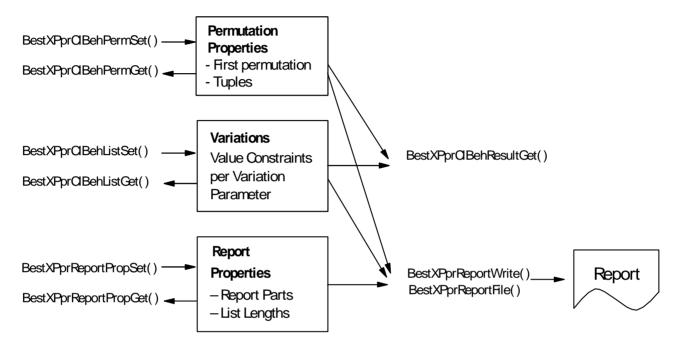

| Programming CI Behavior Permutations               | 150 |

| How to Program CI Behavior Permutations            | 151 |

| Example for Programming CI Behavior Permutations   | 152 |

| Programming RT Behavior Permutations               | 153 |

| How to Program RT Behavior Permutations            | 154 |

| Example for Programming RT Behavior Permutations   | 155 |

| Generating PPR Reports                             | 155 |

| How to Generate PPR Reports                        | 156 |

| Example for Generating PPR Reports                 | 157 |

| Running a PPR Test                                 | 157 |

| How to Run a PPR Test                              | 157 |

| Example for Running a PPR Test                     | 157 |

| Analyzing the Report                                           | 159          |

|----------------------------------------------------------------|--------------|

| Report Header                                                  | 159          |

| Report of Block Permutations                                   | 160          |

| Report of Requester-Initiator Behavior Permutation             | 167          |

| Report of Requester-Initiator Block vs. Requester-Initia       | tor          |

| Behavior Permutation                                           | 171          |

| Further Options and Possibilities                              | 172          |

| Report Listing                                                 | 174          |

| Code Listing                                                   | 185          |

| Synchronizing the Environment                                  |              |

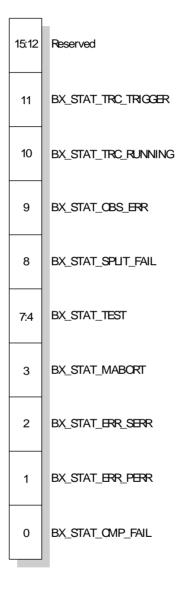

| Card Status Reporting                                          | 191          |

| How to Access the Card Status Register                         | 192          |

| Example for Accessing the Card Status Register                 | 193          |

| Generic Testcard Setup and Power-Up Control                    | 194          |

| How to Program Generic Testcard Properties and Powe<br>Control | er-Up<br>195 |

| Programming the Mailbox                                        |              |

|                                                                | 195          |

| How to Program the Mailbox                                     | 198          |

| Example for Programming the Mailbox                            | 199          |

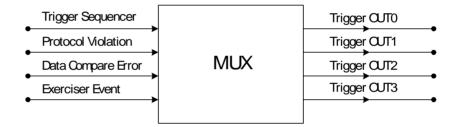

| Programming the Trigger I/O                                    | 199          |

| How to Program the Trigger I/O                                 | 200          |

| Example for Programming the Trigger I/O                        | 202          |

| Programming the Display                                        | 203          |

| Example for Programming the Display                            | 204          |

# About This Guide

| Programming Interface       | The Agilent E2920 PCI-X Series testcards are used for testing PCI-X chips, cards and systems. For this purpose, the testcard allows you to develop test programs by using:                                                                          |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | C-Application Programming Interface (C-API)                                                                                                                                                                                                         |

|                             | The C-API allows you programmable control for the whole system and allows you the integration into existing test environments.                                                                                                                      |

|                             | • Additional functions performed by the PCI-X Permutator and Randomizer software (PPR)                                                                                                                                                              |

|                             | These functions allow you to prepare and perform systematic<br>functional tests at the protocol level, especially exposing PCI-X<br>devices of a computer system to variable stressful PCI-X traffic.                                               |

| Programming Guide Structure | For developing C programs or for using the command line interface of<br>the graphical user interface, this Programmer's Guide gives you good<br>background knowledge of the programming models for the<br>Agilent E2920 PCI-X Series testcards.     |

|                             | The programming guide contains the following sections:                                                                                                                                                                                              |

|                             | • <i>"Programming Overview" on page 11</i> gives basic information about writing C programs, such as where to find the required libraries, compilation and error checking.                                                                          |

|                             | This section also provides information about the first steps to be<br>performed in any C program, such as how the testcard is connected to<br>the control PC and initialized.                                                                       |

|                             | • <i>"Programming the Analyzer" on page 89</i> provides information about programming models for all tasks of PCI-X analysis to monitor the PCI-X bus, to detect specific events, to measure and to evaluate the occurrences of signals on the bus. |

|                             | • " <i>Programming the Exerciser</i> " on page 23 provides information about the programming models for programming the testcard as a initiator and as a target device and for resources shared by both, such as data memory and compare unit.      |

- *"Programming Protocol Permutator and Randomizer Properties" on page 117* provides an overview of the features of the software, and shows how a test program is designed and implemented.

- *"Synchronizing the Environment" on page 189* provides information about the programming models for the available application interfaces, such as trigger I/O sequencer, LED display and mailbox.

# **Documentation Overview**

This section shows you the different types of documents offered by Agilent Technologies and gives you an overview of which documents are available when you work with the Agilent E2929A/B PCI-X Exerciser and Analyzer.

All documents are valid for both Agilent E2929A and Agilent E2929B testcards. The following documents are available:

#### Getting Started Guide • Getting Started Guide

Introduces standard analysis features and provides an example of how to set up the protocol observer.

This guide also gives detailed information about the hardware and interfaces.

#### User's Guides • Agilent E2929A/B Opt. 300 PCI-X Exerciser User's Guide

Provides information on programming the testcard as an initiator and/or target device. It shows you how to actively stimulate the PCI-X bus.

This guide shows how to:

- Initiate data transfers on the PCI-X bus (act as requester-initiator).

- Act as completer-target.

- Handle split completion transactions (act as completer-initiator).

- Handle open requests (act as requester-target).

- Agilent E2929A/B Opt. 100 PCI-X Analyzer User's Guide

Provides information on how to examine the behavior of a PCI-X device on the bus and shows how to perform functional tests such as data compares.

Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer User's Guide

Provides all features that are needed to evaluate and optimize any device under test in terms of the performance.

## • Agilent E2920 PCI-X Series Opt. 320 C-API/PPR Programmer's Guide

Provides information on how to set up test programs using the C functions described in the corresponding C-API/PPR Reference.

#### GUI and C-API/PPR References • Agilent E2929A/B Windows and Dialog Boxes Reference

Provides reference information on all windows and dialog boxes of the Agilent E2920 graphical user interface (GUI).

#### • Agilent E2929A/B Opt. 320 C-API/PPR Reference

Describes all C functions, types and definitions of the application programming interface of the Agilent E2929A/B PCI-X testcard.

This reference also provides the commands and abbreviations that are used in the command line interface (CLI) of the graphical user interface.

• Agilent E2922A/B Opt. 320 C-API/PPR Reference

Describes all C functions, types and definitions of the application programming interface of the Agilent E2922A/B PCI-X testcard.

This reference also provides the commands and abbreviations that are used in the command line interface (CLI) of the graphical user interface.

# **Programming Overview**

The following sections give basic information about the C-API and the PPR software:

- The ways in programming the testcard are shown in "Programming Interfaces" on page 12.

- Where to find the libraries, what you must do when writing C programs, and how to compile the programs depending on the operating system, can be found in "*C Programming Libraries*" on page 13.

- The features of the C-API and the PPR software can be found in "Generic C-API Functionality" on page 14 and "Protocol Permutation and Randomization Functionality" on page 15.

- Error handling macros, which are needed to return error codes of C functions, are explained in *"Exception Handling" on page 15.*

|                                            | The testcard can be programmed in the following ways:                                                                                                                                                                                                                                                                                            |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | <ul> <li>By writing C programs</li> <li>The testcard is shipped with an application programming interface<br/>(the C-API) for the C programming language.</li> <li>See "C Programming Libraries" on page 13.</li> </ul>                                                                                                                          |

|                                            | • By using the command line interface (CLI)                                                                                                                                                                                                                                                                                                      |

|                                            | The CLI provides an easy-to-use graphical user interface for entering commands. Descriptions of the CLI commands can be found in <i>the C-API/PPR Reference</i> , together with their corresponding C function. For more information, refer to "Using the Command Line Interface" in the Agilent E2929A/B Opt. 300 PCI-X Exerciser User's Guide. |

|                                            | <ul> <li>By writing TCL programs</li> </ul>                                                                                                                                                                                                                                                                                                      |

|                                            | See file <instdir>\PCIX\src\tcl\readme.txt.</instdir>                                                                                                                                                                                                                                                                                            |

| Hints for programming on 64 bit<br>systems | If you plan to run the PCI-X software under 64 bit Itanium systems, you should read the following.                                                                                                                                                                                                                                               |

|                                            | Targeted are currently the 64 bit Microsoft .NET Server OSes.                                                                                                                                                                                                                                                                                    |

|                                            | To install, you need a separate installation file, named setup<br>64.exe, located in the CD's $ia64$ directory. Do not install the 32<br>bit setup.exe.                                                                                                                                                                                          |

|                                            | On 64bit Itanium systems the following is true:                                                                                                                                                                                                                                                                                                  |

|                                            | • Kernel mode:                                                                                                                                                                                                                                                                                                                                   |

|                                            | Drivers always need to be 64 bit drivers; 32 bit drivers wont work.<br>Especially, this means that you can't use the existing 32 bit drivers.<br>Our 64 bit drivers are named $b_2kpci_64.sys$ , $b_2khif_64.sys$ ,<br>$b_usb_64.sys$ and $b_usbgen_64.sys$ .                                                                                    |

|                                            | • User mode:                                                                                                                                                                                                                                                                                                                                     |

|                                            | If you are starting an application, the .exe (and all needed dlls) need to<br>be either all 32 bit files or all need to be 64 bit files, i.e. you cannot mix<br>them. For example a 64 bit .exe cannot use a 32 bit dll.                                                                                                                         |

|                                            | Our 64-bit dlls always have the suffix "xp64", e.g. capixp64.dll (instead of capikk.dll in 32 bit mode).                                                                                                                                                                                                                                         |

**Programming Interfaces**

• The PCI-X GUI always only runs in 32bit mode (so they alway needs the corresponding 32 bit dlls).

If you want to write your own C-API programs, you can use the provided 64bit dlls though and run your program as 64 bit executable (32 bit mode is forced only when using the GUI).

## **C** Programming Libraries

The Installation Wizard stores by default the library files, user documentation and programming examples to the PC. You can also develop your test program on a different PC (in the "Demo/Offline Mode" of the software) and later upload your application to the control PC.

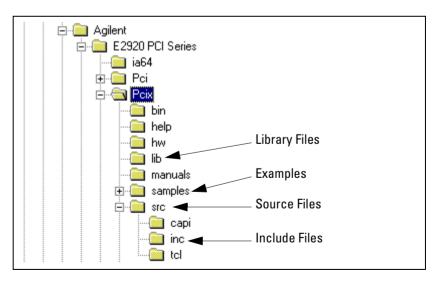

**Directory Structure** All required files are automatically installed with the control software and can be found in the subdirectories of the Agilent PCI-X Series home directory. The following figure shows the directory structure on a Windows NT system.

The home directory is:

C:\Program Files\Agilent\E2920 PCI(X) Series 1.4\PCIX\

When developing C programs for the testcard, you need to:

• Include only the header file xpciapi.h into your program, because it includes all necessary header files.

|                     | • Enter the paths to include files, library files, and/or source files into the directory settings of your developing environment.                                                                                                                                                                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | <ul> <li>For Windows 2000, you also have to include xcapikk.lib to the<br/>developing environment.</li> </ul>                                                                                                                                                                                                                                                                                    |

|                     | <ul> <li>For Windows NT, you also have to include xcapint.lib to the<br/>developing environment.</li> </ul>                                                                                                                                                                                                                                                                                      |

| Examples            | Many ready-to-use example programs can be found in the <b>samples</b> directory. The <b>user documentation</b> for hardware, software, and options uses many of these examples to explain the functions.                                                                                                                                                                                         |

| Platform-Dependence | All sample programs can be compiled with Microsoft ® VC 6.0.<br>Communication with E2920 Series PCI-X testcards uses the E2920 Series<br>C-API. The C-API is the interface for testcard communication. The C-API<br>is available in binary form for a number of operating systems, and as<br>compilable source code. A workspace for compiling the CAPI is available<br>under src\capi\capi.dsw. |

## **Generic C-API Functionality**

The C-API is used to program all analyzer, exerciser and performance optimizer functionalities.

For all features of the testcard, refer to:

- Agilent E2929A/B Getting Started Guide

- Agilent E2929A/B Opt. 300 PCI-X Exerciser User's Guide

- Agilent E2929A/B PCI-X Analyzer User's Guide

- Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer User's Guide

## **Protocol Permutation and Randomization Functionality**

The PCI-X Protocol Permutation and Randomization software adds functions to the C-API for preparing and performing systematic functional tests at the protocol level, especially tests for exposing PCI-X devices of a computer system to variable stressful PCI-X traffic.

For more information on the PPR functionality, refer to "Introduction" on page 118.

## **Exception Handling**

Try blocks are an efficient way of catching errors in a series of C-API function calls and are particularly useful for situations where some cleanup is required after an error occurs.

Error Checking

The BX\_TRY() macro in the BX\_TRY\_BEGIN {} section checks if there was an error in the most recent call. If an error occurs, processing in the TRY block stops and the program proceeds with the BX\_TRY\_CATCH {} section.

All functions in TRY macros must return bx\_errtype..

Error Handling In case of an error, the easiest action is to print out the error string.

To get the error string, use the following function calls:

- BestXLastErrorStringGet(handle) if you know the handle (handlebased error checking).

- BestXErrorStringGet(error number) if you know the error number (non-handle-based error checking)

### **Example with Handle-Based Error Checking**

The principle of exception handling is shown by means of the following example:

```

bx errtype SomeFunction(bx handletype handle)

{

BX TRY VARS NO PROG; /* declares all necessary variables

/* starts a try block

BX TRY BEGIN

{

// API calls using the BX TRY macro (returning bx errtype)

BX TRY(BestXPing(handle));

BX TRY(BestXDisplayStringWrite(handle, "PCIX"));

}

BX TRY CATCH

/* starts the catch block

/* (optional)

{

// errorhandling (cleanup,ignore and/or handle error)

// (optional)

BX TRY RET=BX E OK;

/* ignores the error;

/* you can also switch over

/* BX TRY RET and react to

/* different errors.

printf("%s\n", BestXLastErrorStringGet(handle));

}

BX ERRETURN(BX TRY RET)

/* the reason for the failure

/* you can evaluate this macro

}

```

### **Non-Handle-Based Error Checking**

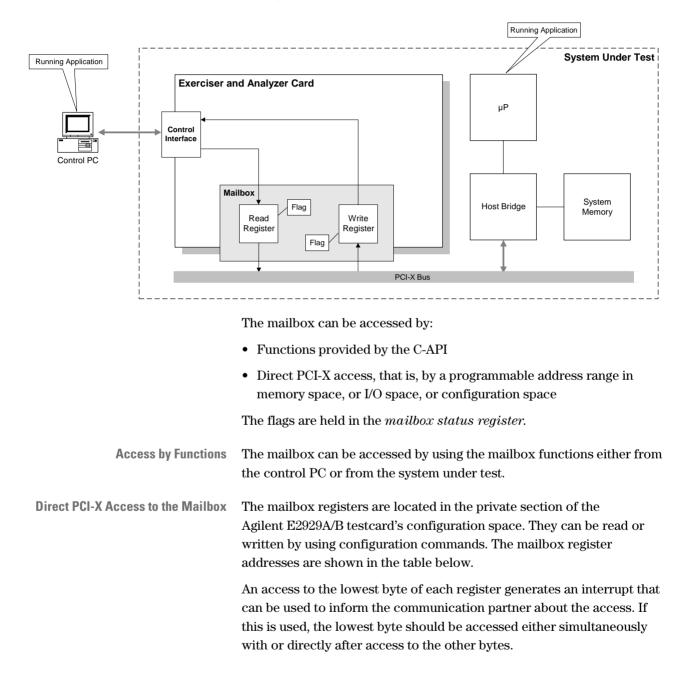

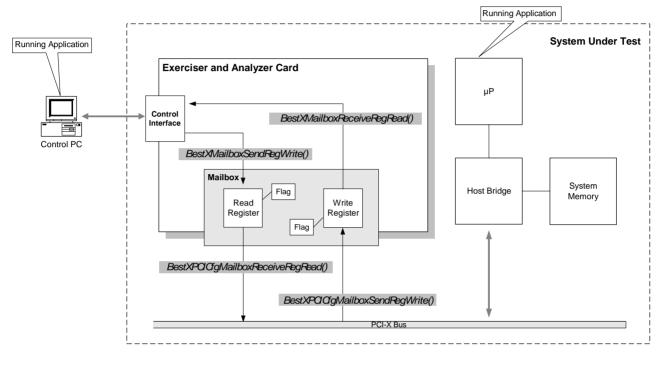

The following functions do not provide handles, therefore they cannot be used with handle-based error checking methods:

- BestXDevIdentifierGet()

- BestXPCICfgMailboxReceiveRegRead()

- BestXPCICfgMailboxSendRegWrite()

| Handle Initialization | The following function initializes the handle. The handle is valid on<br>this function returns the handle successfully: |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|--|

|                       | • BestXOpen()                                                                                                           |  |

| Calling the Macro     | This macro can be called in the following way:                                                                          |  |

|                       | <ul> <li>BX_TRY(BestDevIdentifierGet(vendor_id, device_id, number, &amp;devid));</li> </ul>                             |  |

|                       |                                                                                                                         |  |

For error codes, refer to "bx\_errtype" in the *C-API/PPR Programming Reference*.

## **Getting Started**

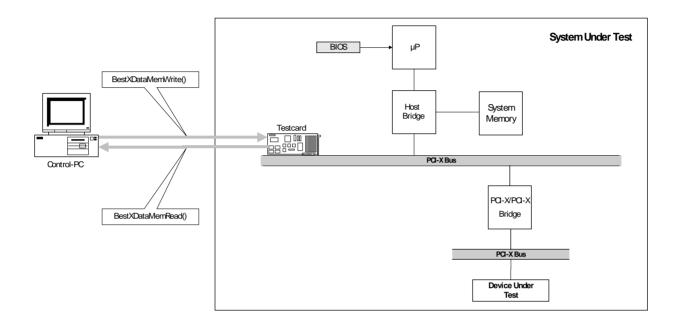

The first step in running tests on the testcard is to initialize the testcard and its connections. The testcard can be controlled via PCI-X port, RS-232 serial interface or Fast Host Interface.

Some typical initialization routines for each type of control connection are shown in *"Example for Getting Started" on page 20.*

**PCI-X Port** The testcard communicates via the PCI-X bus through its configuration space.

No system resources are required to program the testcard. The PCI-X port is especially useful when the DUT controls the testcard in order to run parallel and synchronized tests. This port should not be used if changing the system by the testcard is not allowed (for example, for memory mapping).

- **RS-232 Serial Interface** The RS-232 serial interface of the Agilent E2929A/B testcard provides an easy-to-use control interface, which is available on all PCs and notebook computers. It can be run at 9600, 19200, 38400, and 57600 baud.

- **USB Port** The USB port of the Agilent E2929A/B testcard can be used to connect more than 4 testcards to one host without using PCI-X connections. With an USB hub, as many as 256 PCI-X testcards can be controlled simultaneously.

The first USB connection to a testcard to be found is assigned to "0", the second to "1", and so forth. The order in which the cards are found is not predictable. To see which card is connected to the session, use BestXPing and watch the LEDs (after the BestXOpen call).

| Fast Host Interface Port | The Fast Host Interface port of the Agilent E2929A/B testcard provides<br>an easy-to-install connection to the control PC with higher throughput<br>than an RS-232 interface in both read and write directions. |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | The control PC must be equipped with the Fast Host Interface card (delivered with the PCI-X Analyzer) and connected to the parallel port of the testcard.                                                       |

| Specification            | Maximum transfer rate: 4 MB/s (using the Fast Host Interface of the Agilent E2929A/B testcard).                                                                                                                 |

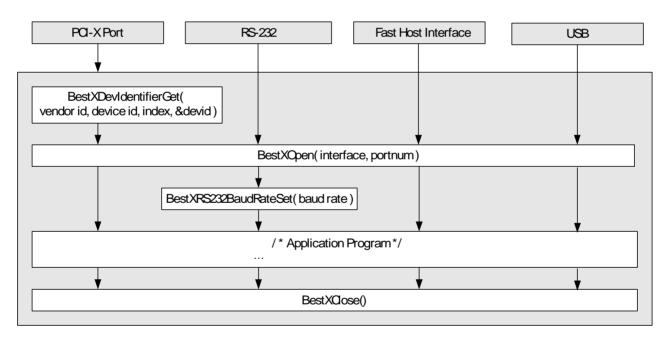

### How to Get Started

The following figure shows which commands would be used to operate the testcard at different ports. This figure also shows the integration of these functions into the test program.

Programming Steps The tes

The testcard is initialized as follows:

- **1** Open a session with *BestXOpen*. This call:

- Initializes the session data structures.

- Establishes the connection to the testcard and checks for valid card-type and revision.

- Returns the session handle on success.

**NOTE** If the **PCI-X Bus** is used as the controlling interface port, use *BestXDevIdentifierGet* to get the device number of the testcard, which is is used in *BestXOpen* for device identification.

If the **RS-232** serial interface is used, you have to set the baud rate with *BestXRS232BaudRateSet*.

- **2** After inserting the application code, close the session with *BestXClose*. This call:

- Frees the session data structures.

- Disconnects from the testcard.

### **Example for Getting Started**

```

Task

Write a C-API application that writes the text "Hello World" to the

hexadecimal display on the E2929A card.

NOTE

The following example can be used as framework for all further code

fragments using the C-API in this document.

Implementation

#include "xpciapi.h"

int main(int argc, char* argv[])

{

int i;

BX TRY VARS NO PROG;

/* Enter additional local variable declarations here */

bx handletype handle;

BX TRY BEGIN

{

/* Open the communication session to testcard, initialize */

/* internal structures */

BX TRY(BestXOpen(&handle, BX PORT RS232, BX PORT COM1));

/* If using RS232, set baud rate: */

BX TRY(BestXRS232BaudRateSet(handle, BX BD 57600));

/* Insert here your C-API calls */

/* For example:*/

/* Write "Hello World" to the display.*/

for (i=0;i<10;i++)

{

BX TRY (BestXDisplayStringWrite(handle, "HEL-"));

BX_TRY (BestXDisplayStringWrite(handle, "HEL\\"));

BX TRY (BestXDisplayStringWrite(handle, "HEL|"));

BX TRY (BestXDisplayStringWrite(handle, "HEL/"));

}

/* Close the session to deallocate memory. */

BX TRY(BestXClose(handle));

}

BX TRY CATCH

{

printf(BestXErrorStringGet(BX TRY RET));

/* cleanup, if necessary */

BX ERRETURN(BX TRY_RET);

}

```

**NOTE** This program can also be found under <INST\_DIR>\ PCIX\Samples\HelloWorld.cpp.

### **Benefits**

When setting up tests, you can take advantage of the following features of the Exerciser and Analyzer and the PCI-X Permutator and Randomizer software:

#### • Creating controlled protocol corner cases

The software makes it possible to expose device or system under test to corner case traffic, to add system and parity errors, to assert and deassert signal lines and so on.

Tests can be set up that add as many Exerciser and Analyzers as required and let them transfer data blocks repeatedly to generate enough traffic to stress the PCI-X system.

#### • Data-integrity testing

The software makes it possible to use the Exerciser and Analyzer memory functions to comfortably write, read and compare data blocks.

#### • Emulating typical peripheral traffic

The software makes it possible to substitute test devices with Exerciser and Analyzers. Testcards can be set up to behave like any device. The memory is programmable with any content. There is no need to exchange devices in the system for testing reasons to get "realistic" traffic.

The PCI-X Permutator and Randomizer software intensifies the possibilities by systematically varying transfer parameters to examine protocol corner cases.

#### • Storing and analyzing bus traffic

The software makes it possible to find illegal behavior on protocol and signal level using advanced listers (waveform viewer, bus cycle lister, transaction lister) of the (optional) graphical user interface of Exerciser and Analyzer. These listers allow a detailed analysis of all events that have occurred on the considered bus.

#### • Stressing on multiple PCI/PCI-X buses

The software makes it possible to use multiple testcards to generate stress traffic from one bus system to another over PCI/PCI-X-to-PCI-/PCI-X bridges.

#### • Deterministic and reproducible tests

In contrast to PCI-X traffic generated by other test devices, the generated variations are deterministic and reproducible. This guarantees coverage and reproducible tests. The permutation progress can be read out on block level or block page level. In the case of an error or a bus hang, exactly the same behavior can be repeated for reproduction of the error. Alternatively, the test can be continued after that error.

## • PCI-X protocol behavior permutations within programmable constraints

The software makes it possible to specify the values to be varied for each requester-initiator, completer-target, completer-initiator, and requester-target separately. Thus, testing time can be reduced by focusing on cases of interest. Problems can be quickly isolated.

#### Detailed report

The software provides a printable report, which shows which protocol behaviors are completely permutated against which other protocol behaviors after how many of data transfers.

#### • Predictable testing time

The test's run time estimated by the PCI-X Protocol Permutation and Randomization can also be written to the report.

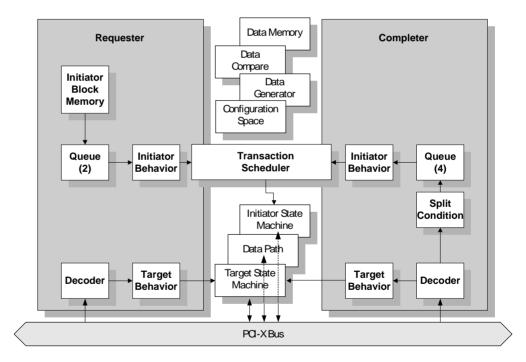

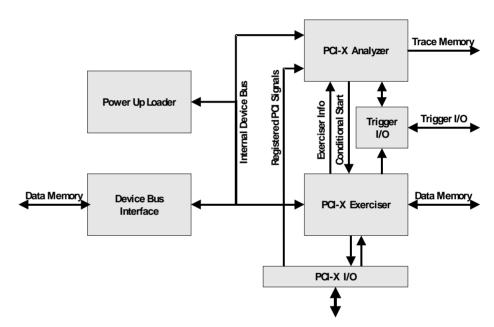

# Programming the Exerciser

The PCI-X Exerciser testcard can simulate a requester-initiator, a completer-target, a completer-initiator or a requester-target device or all together at the same time. All these can be controlled by functions of the C-API.

This enables the testcard to emulate and/or test any device in your system under test.

The following figure shows the programmable components of the testcard's exerciser.

The concept for programming the exerciser is as follows:

Defining Blocks

1. Defining up to 256 requester-initiator data blocks

The blocks describe what data is transferred over the PCI-X bus.

Each block transaction coming out of the requester-initiator block

memory is put into one of two queues.

See "Programming Requester-Initiator Block Transfers" on page 30.

#### **Defining Behaviors** 2. Defining requester-initiator (RI) behaviors

The behaviors describe **how** data transferred over the PCI-X bus is executed.

If any target replies to a transfer and requests a split transaction, the data block attributes are moved internally to the split transaction map for further use. The split transaction map can manage up to 32 split transactions.

When completing split transactions, the requester-target behaviors are used to control the transfer.

The transaction that will be given a split response is determined by the split response condition.

See "Programming the Behavior of Block Transfers" on page 35.

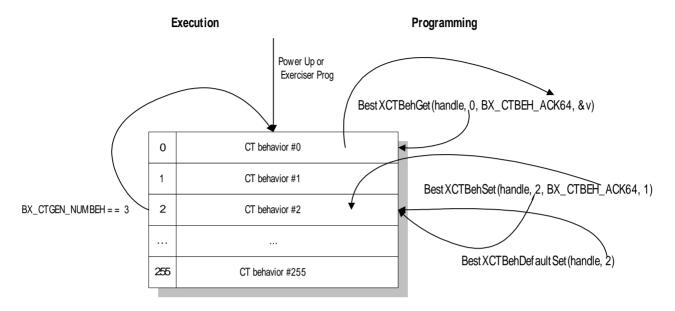

#### 3. Defining completer-target (CT) behaviors

The completer-target behaviors control how the target reacts to requests. The completer-target behaviors control, for example, whether a target is able to reply to a transfer with a split response.

The completer-target can manage up to five transactions.

See "Programming the Completer-Target Behavior" on page 48 for more information.

#### 4. Setting the split response condition

To identify a request that will be given a split response, the split response condition property must be set.

See "Programming a Split Condition" on page 53 for more information.

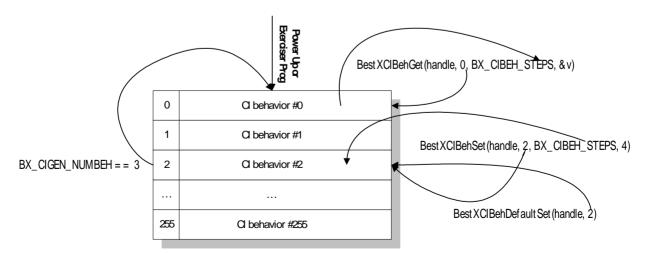

#### 5. Defining completer-initiator (CI) behaviors

The completer-initiator behaviors define when and how requests are completed that have been replied to with a split response.

See "*Programming the Completer-Initiator Behavior*" on page 57 for more information.

#### 6. Defining requester-target (RT) behaviors

When completing split transactions, the requester-target behaviors are used to control the transfer.

See "Programming the Requester-Target Behavior" on page 63 for more information.

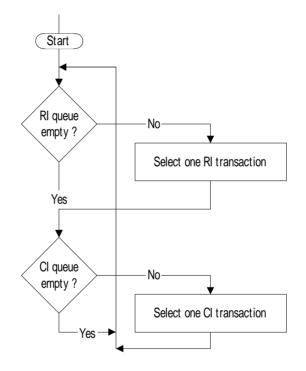

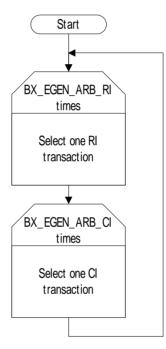

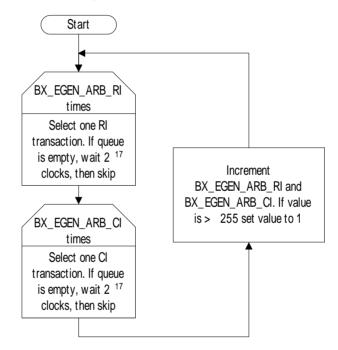

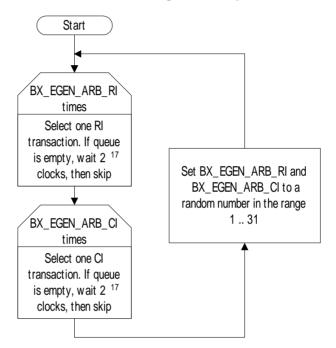

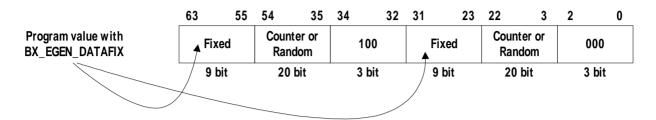

#### 7. Programming the transaction scheduler

The transaction scheduler decides which transactions (completerinitiator or requester-initiator transactions) are performed.

See "Scheduling Block Transfers and Split Completions" on page 68 for more information.

8. Programming **completer-target (CT) decoders** for different types of accesses (I/O, memory, configuration cycles, expansion ROM) and the **requester-target decoder** for decoding split completion transactions.

See "Programming a Target Decoder" on page 41 for more information.

- **Resources** 9. Defining the data to be transferred All data needed for performing transactions is supplied by the onboard **data memory** or from the onboard **real-time generator**.

- **NOTE** The **data path** is shared by initiator and target as a common resource.

See "Programming the Data Memory" on page 81 and "Programming the Data Generator" on page 73 for more information.

10. Performing data compare

The real-time **data compare** unit is used to compare data that is written to the memory against the actual memory content. Data compare can also be performed on the data generator.

11. Accessing the configuration space of the testcard

The configuration space of the testcard (public and private section) can be employed as a resource. In order to simulate all the possible types of PCI-X devices, the configuration space header of the testcard is freely programmable.

See "Programming the Configuration Space" on page 45 for more information.

The exerciser further allows you to generate PCI-X interrupts. See *"Programming PCI-X Interrupts" on page 85.*

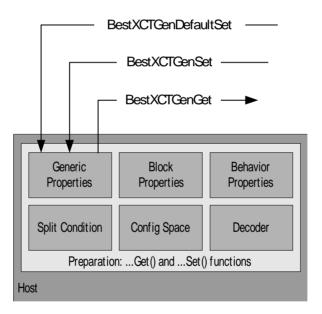

### **Reading From and Writing To the Memories**

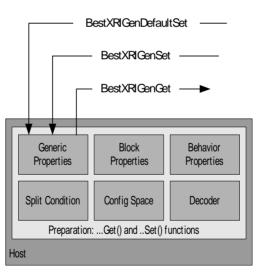

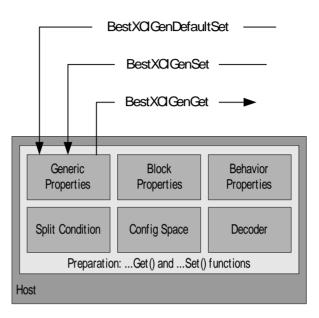

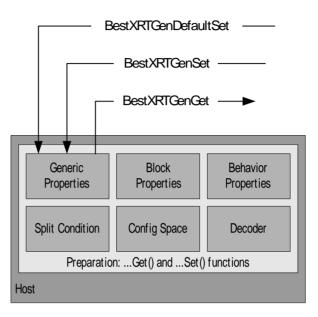

The C-API uses preparation functions (...Get() and ...Set() functions) for reading and writing properties from and to the host. These functions do not access the hardware.

To access the hardware, use the ...Read(), ...Prog(), or ...Write() functions.

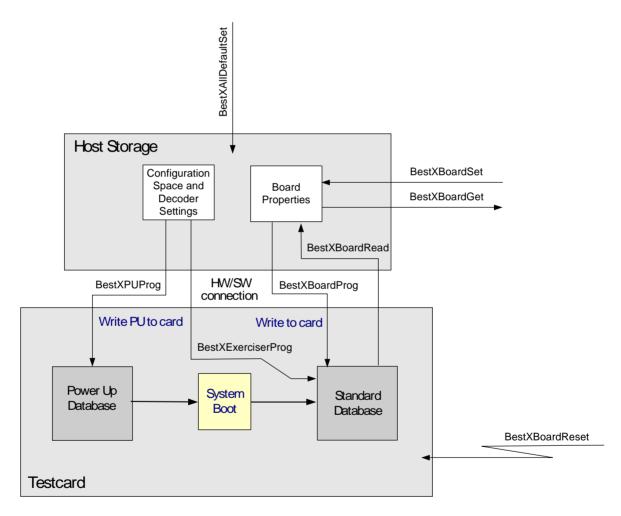

The following figure shows the C-API architecture.

| Host                  |                        |                           |

|-----------------------|------------------------|---------------------------|

| Preparatio            | on:Get() andSet()      | functions                 |

| Generic<br>Properties | Block<br>Properties    | Behavior<br>Properties    |

| Split Condition       | Config Space           | Decoder                   |

|                       | Card:Read() andF       | Prog() functions<br>PCI-X |

|                       |                        |                           |

| DUT                   | ¥ ¥                    | •                         |

|                       | Firmw are<br>Hardw are |                           |

## Downloading Settings and Running the Exerciser

This section describes global exerciser functions.

| Downloading            | All available properties first are programmed to the host storage. If you set all properties, you have to write them to the testcard.<br>To write all settings to the testcard, use <i>BestXExerciserProg</i> .                                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reading                | To read settings from the testcard, use <i>BestXExerciserRead</i> . This function can either read the entire memory or only generic properties.                                                                                                            |

| Running the Exerciser  | To run the exerciser, use <i>BestXExerciserRun</i> .                                                                                                                                                                                                       |

| Stopping the Exerciser | To stop the exerciser, use <i>BestXExerciserStop</i> , where the current transaction will be completed.                                                                                                                                                    |

| Exerciser Reset        | To reset all bus state machines (initiator and target) and to clear the requester-initiator intention, use <i>BestXExerciserReset</i> .                                                                                                                    |

| CAUTION                | The call <i>BestXExerciserReset</i> might lead to a behavior that does not conform to the protocol. All state machines are reset, regardless of their current state. Hence, the bus state will be unclear. This call should only be used if a bus is hung. |

### **Programming the Exerciser as a Requester-Initiator Device**

To program the testcard's exerciser as a requester-initiator device means programming the testcard to initiate data transfers via PCI-X bus either to a target device under test, or to the testcard's own target (completer-target). The latter test case can be used to increase bus load.

The following need to be programmed for the testcard to perform data transfer:

1. Generic requester-initiator properties

Generic requester-initiator properties determine the behavior of the testcard and are valid during a complete exerciser run. They determine, for example, whether the requester-initiator should start immediately or conditionally after a trigger event.

See "Programming Generic Requester-Initiator Properties" on page 29.

2. The requester-initiator transactions to be performed

Transactions can be summarized into blocks. The properties of each block and its transactions, such as PCI-X bus address, number of dwords to be transferred or the bus command, are programmed in the block transfer memory.

See "Programming Requester-Initiator Block Transfers" on page 30.

3. The behaviors to be used with the transactions

The behaviors determine how the transactions should be executed, for example, whether and how often the requester-initiator disconnects its current sequence. This information is located in the requester-initiator behavior memory.

See "Programming the Behavior of Block Transfers" on page 35.

4. The data to be used for the transactions

For this purpose, the data memory and the data generator can be used as a data resource by the requester-initiator.

See "Programming the Data Memory" on page 81 and "Programming the Data Generator" on page 73.

5. The way of running the exerciser

See "Downloading Settings and Running the Exerciser" on page 27.

### Programming Generic Requester-Initiator Properties

Generic requester-initiator properties are valid for a complete exerciser run.

You can program the following generic requester-initiator properties:

- How many block transfers were programmed (BX\_RIGEN\_NUMBLK) Valid values are 1 ... 256.

- How often the block transfers will be repeated (BX\_RIGEN\_REPEATBLK) Valid values are 1 ... 0xfffffff, BX\_RIGEN\_REPEATBLK\_INFINITE

- The number of valid RI-behaviors (BX\_RIGEN\_NUMBEH) Valid values are 1 ... 256.

- The values for the seven skip registers (BX\_RIGEN\_SKIP\_REG1 ... BX\_RIGEN\_SKIP\_REG7) Valid values are 0 ... 1023.

### How to Program Generic Requester-Initiator Properties

The following figure shows the functions used to program the generic requester-initiator properties.

**Programming Steps**

- To set generic requester-initiator property values on the host:

- **1** Set all generic requester-initiator properties to default values with *BestXRIGenDefaultSet*.

- 2 Set each property with *BestXRIGenSet* to the appropriate value. To get the value of one property, use *BestXRIGenGet*.

### Example for Programming Generic Requester-Initiator Properties

Task Define that two requester-initiator behaviors should be executed twice.

Implementation /\* Define that two programmed block transfers are repeated twice \*/

BX\_TRY(BestXRIGenSet(handle, BX\_RIGEN\_NUMBLK, 2)); BX TRY(BestXRIGenSet(handle, BX RIGEN REPEATBLK, 2));

/\* Define that five behaviors for the block transfers are programmed  $\ast/$

BX\_TRY(BestXRIGenSet(handle, BX\_RIGEN\_NUMBEH, 5));

### Programming Requester-Initiator Block Transfers

A requester-initiator block transfer means to transfer a contiguous block of data from one place to the other. A block transfer is specified by:

• Read/Write operation

| Operation | Source               | Destination          |

|-----------|----------------------|----------------------|

| Read      | physical bus address | exerciser data       |

| Write     | exerciser data       | physical bus address |

- The bus command:

- Memory read DWORD or memory write

- I/O read or write, configuration read or write

- Memory read block or memory write block

- Split completion

- Interrupt acknowledge

- Alias to memory read or write block

- Reserved cycle

- Size (number of bytes (up to 4 GB))

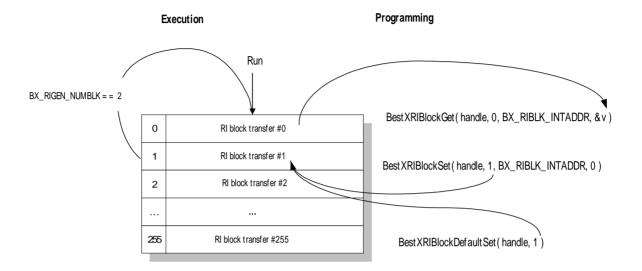

The information for a block transfer is stored in the requester-initiator block memory. This memory can hold up to 256 block transfer entries.

### **How to Program Block Transfers**

To program requester-initiator block transfers:

**1** Set all entries of the requester-initiator block memory to default values.

Use BestXRIBlockDefaultSet.

**2** Program each block transfer to one line of the requester-initiator block transfer memory. Each transfer is specified by several block transfer properties.

For each block transfer property to be programmed, use *BestXRIBlockSet*.

To query the value of a requester-initiator block property, use *BestXRIBlockGet*.

- **3** Set all generic requester-initiator properties to default values. Use *BestXRIGenDefaultSet*.

- 4 Define how many times each block transfer should be executed.

- First, set all generic requester-initiator properties to default values with *BestXRIGenDefaultSet*

- Then, use *BestXRIGenSet* to set the requester-initiator generic property BX RIGEN NUMBLK to the appropriate value (1 ... 256).

For more information about generic requester-initiator properties, see "Programming Generic Requester-Initiator Properties" on page 29.

**5** Define how often the previously specified block transfers should be executed.

Use *BestXRIGenSet* and set the requester-initiator generic property BX\_RIGEN\_REPEATBLK to the appropriate value. Valid values are BX\_RIGEN\_REPEATBLK\_INFINITE, 1 ... 0xfffffff. The following figure shows the memory design, the available functions to program the requester-initiator block memory, and the execution order.

- **6** Download all exerciser settings and properties to the hardware with *BestXExerciserProg.*

- 7 Start the transfer(s) with *BestXExerciserRun*.

### **Examples for Programming Block Transfers**

- Task (Example 1) The task is as follows:

- Program the E2929A so that it starts two block transfers:

- First block transfer: One memory read block of 495 bytes from bus address 100030fd\h and

- Second block transfer: One I/O write of 7 bytes to bus address 1000ff\h.

Use the internal address starting at 0\h.

| Implementation (Example 1) | <pre>/* Set the number of block transfers to be executed and how often they should be executed */</pre>                                                          |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                            | <pre>BX_TRY(BestXRIGenDefaultSet(handle);<br/>BX_TRY(BestXRIGenSet(handle, BX_RIGEN_NUMBLK, 2));<br/>BX_TRY(BestXRIGenSet(handle, BX_RIGEN_REPEATBLK, 1));</pre> |  |

|                            | /* Program a block transfer to memory line 0*/                                                                                                                   |  |

|                            | <pre>BX_TRY(BestXRIBlockDefaultSet(handle, 0));<br/>BX_TRY(BestXRIBlockSet(handle, 0, BX_RIBLK_BUSADDR_LO,<br/>0x100030fdUL));</pre>                             |  |

|                            | <pre>BX_TRY(BestXRIBlockSet(handle, 0, BX_RIBLK_BUSCMD,<br/>BX_RIBLK_BUSCMD_MEM_READBLOCK));</pre>                                                               |  |

|                            | <pre>BX_TRY(BestXRIBlockSet(handle, 0, BX_RIBLK_NUMBYTES, 495));<br/>BX_TRY(BestXRIBlockSet(handle, 0, BX_RIBLK_INTADDR, 0));</pre>                              |  |

|                            | /* Program a block transfer to memory line 1 */                                                                                                                  |  |

|                            | <pre>BX_TRY(BestXRIBlockDefaultSet(handle, 1));</pre>                                                                                                            |  |

|                            | <pre>BX_TRY(BestXRIBlockSet(handle, 1, BX_RIBLK_BUSADDR_LO,<br/>0x1000ffUL));</pre>                                                                              |  |

|                            | <pre>BX_TRY(BestXRIBlockSet(handle, 1, BX_RIBLK_BUSCMD,<br/>BX_RIBLK_BUSCMD_IO_WRITE));</pre>                                                                    |  |

|                            | <pre>BX_TRY(BestXRIBlockSet(handle, 1, BX_RIBLK_NUMBYTES, 7));<br/>BX_TRY(BestXRIBlockSet(handle, 1, BX_RIBLK_INTADDR, 0));</pre>                                |  |

|                            | /* Write the settings to the testcard and run the exerciser $^{*/}$                                                                                              |  |

|                            | BX_TRY(BestXExerciserProg(handle));<br>BX_TRY(BestXExerciserRun(handle));                                                                                        |  |

| Task (Example 2)           | The task is as follows:                                                                                                                                          |  |

|                            | • Program the same block transfers as in example 1.<br>This time:                                                                                                |  |

|                            | <ul> <li>Use the data generator as resource.</li> </ul>                                                                                                          |  |

|                            | <ul> <li>Put the memory read with 531 bytes into queue B and the I/O w<br/>into queue A.</li> </ul>                                                              |  |

- Set the *relaxorder* and *nosnoop* bits.

- Let the exerciser repeat the transfers 5 times.

write

```

Implementation (Example 2)

/* Define that two block transfers are programmed that are repeated

5 times */

BX TRY (BestXRIGenSet (handle, BX RIGEN NUMBLK, 2));

BX TRY (BestXRIGenSet (handle, BX RIGEN REPEATBLK, 5));

/* Program a block transfer to memory line 0*/

BX TRY(BestXRIBlockDefaultSet(handle, 0));

BX TRY(BestXRIBlockSet(handle, 0, BX RIBLK BUSADDR LO,

0x100030fdUL));

BX TRY(BestXRIBlockSet(handle, 0, BX RIBLK BUSCMD,

BX RIBLK BUSCMD MEM READBLOCK));

BX TRY(BestXRIBlockSet(handle, 0, BX RIBLK NUMBYTES, 531));

BX TRY(BestXRIBlockSet(handle, 0, BX RIBLK INTADDR, 0));

BX TRY (BestXRIBlockSet (handle, 0, BX RIBLK RELAXORDER, 1));

BX TRY(BestXRIBlockSet(handle, 0, BX RIBLK NOSNOOP, 1));

BX TRY(BestXRIBlockSet(handle, 0, BX RIBLK RESOURCE,

BX RIBLK RESOURCE DATAGEN));

BX TRY(BestXRIBlockSet(handle, 0, BX RIBLK QUEUE,

BX RIBLK QUEUE B));

/* Program a block transfer to memory line 1 */

BX TRY(BestXRIBlockDefaultSet(handle, 1));

BX TRY (BestXRIBlockSet (handle, 1, BX RIBLK BUSADDR LO,

0x1000ffUL));

BX TRY(BestXRIBlockSet(handle, 1, BX RIBLK BUSCMD,

BX RIBLK BUSCMD IO WRITE));

BX TRY(BestXRIBlockSet(handle, 1, BX RIBLK NUMBYTES, 7));

BX TRY (BestXRIBlockSet (handle, 1, BX RIBLK INTADDR, 0));

BX TRY(BestXRIBlockSet(handle, 1, BX RIBLK RELAXORDER, 1));

BX TRY (BestXRIBlockSet (handle, 1, BX RIBLK NOSNOOP, 1));

BX TRY(BestXRIBlockSet(handle, 1, BX RIBLK RESOURCE,

BX_RIBLK_RESOURCE_DATAGEN));

BX TRY(BestXRIBlockSet(handle, 1, BX RIBLK QUEUE,

BX RIBLK QUEUE A));

/* Write the settings to the testcard and run the exerciser */

BX TRY(BestXExerciserProg(handle));

BX TRY(BestXExerciserRun(handle));

```

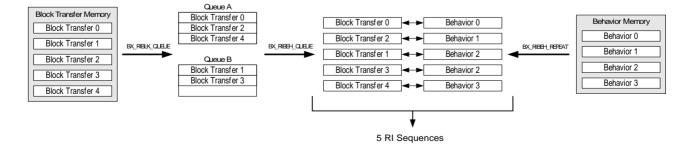

### Programming the Behavior of Block Transfers

The requester-initiator behaviors define how block transfers are executed. In particular, behaviors control the partitioning of blocks into sequences and the reordering of blocks.

The requester-initiator behaviors are stored in the requester-initiator behavior memory. Each memory line holds one behavior for the block transfer. When the exerciser is started, one behavior is assigned to one block transfer.

The following figure shows the correlation between block transfers and behaviors, and how to generate sequences.

How to create sequences in detail is shown in the following figure by means of an example.

Each requester-initiator behavior has the following programmable properties.

• Requester-initiator queue (BX\_RIBEH\_QUEUE)

Valid values are BX\_RIBEH\_QUEUE\_A, BX\_RIBEH\_QUEUE\_B, BX\_RIBEH\_QUEUE\_NEXT.

By setting this behavior and the corresponding block property (BX\_RIBLK\_QUEUE), you can determine if blocks get executed in order or if they bypass each other.

- Fixed tag number or any free tag if possible (BX\_RIBEH\_TAG)

- Byte count for the sequence ( $BX_RIBEH_BYTECOUNT$ )

Valid values are 1 ... 4096.

This property partitions the value of the block transfer property BX\_RIBLK\_NUMBYTES into sequences of a maximum length of 4096 bytes.

• Disconnect at ADB number N (BX\_RIBEH\_DISCONNECT)

This property allows you to break a sequence into multiple transactions. The requester-initiator disconnects at every N-th allowable disconnect boundary (ADB). Typically, the requesterinitiator will not disconnect, because the data transfer will have been completed when it requests a transaction.

When the requester-initiator disconnects a sequence, it resumes the disconnected sequence. It is not possible to execute some other action in between.

Clock delay before assertion of REQ# (BX\_RIBEH\_DELAY)

This property allows you to vary latencies between transactions. Sometimes the minimum achievable latency to the next requesterinitiator transaction is restricted by the most recent event and sometimes by the data path configuration.

• Number of address steps (BX RIBEH STEPS)

The number of address steps is the number of clock cycles between the assertion of GNT# and the assertion of FRAME# plus two clock cycles. These two clock cycles are designed into the register-to-register interface of PCI-X.

- 64-bit data transfer request (BX\_RIBEH\_REQ64) Valid values are:

- 1 = Assert the REQ64# signal

- 0 = don't assert the REQ64# signal

- Number of repeats (BX\_RIBEH\_REPEAT) The current behavior is repeated N times before the next behavior is

- Tag number to be used for this sequence (BX\_RIBEH\_TAG) Valid values are 0 ... 31.

- Number of clock cycles that REQ# is asserted after the address phase (BX\_RIBEH\_RELREQ)

Valid values are  $1 \dots 2047$ .

used. Valid values are 1 ... 256.

• Number of the skip register (BX\_RIBEH\_SKIP)

Valid values are 1  $\dots$  7, BX\_RIBEH\_SKIP\_NO.

The number is used if this behavior was repeated. The value of the selected skip register is then added to the start address of the next sequence.

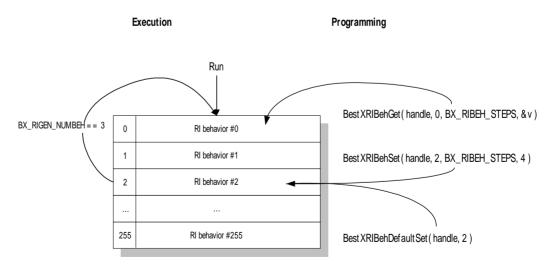

#### How to Program the Behavior of Block Transfers

To program the behavior of requester-initiator block transfers:

**1** Set all entries of the requester-initiator behavior memory to default values.

Use BestXRIBehDefaultSet.

**2** Program each behavior to one line of the requester-initiator behavior memory. Each behavior is specified by several behavior properties.

For each behavior property to be programmed, use *BestXRIBehSet*.

To query the value of a requester-initiator behavior property, use *BestXRIBehGet*.

- **3** Define how many behaviors should be executed.

- First, set all generic requester-initiator properties to default values with *BestXRIGenDefaultSet*.

- Use *BestXRIGenSet* and set the requester-initiator generic property BX\_RIGEN\_NUMBEH to the appropriate value (1 ... 256).

For more information about generic requester-initiator properties, see "Programming Generic Requester-Initiator Properties" on page 29.

**4** Define how often the current behavior is applied before the next behavior is used.

Use *BestXRIBehSet* and set the requester-initiator generic property BX RIBEH REPEAT to the appropriate value. Valid values are 1 ... 256.

The following figure shows the memory design, the available functions to program the requester-initiator block memory, and the execution order.

- **5** Download all exerciser settings and properties to the hardware with *BestXExerciserProg.*

- **6** Start the transfer(s) with *BestXExerciserRun*.

# Example for Programming the Behavior of Block Transfers

- **Task** Perform the following task:

- Program the same block transfers as in "Task (Example 2)" on page 33.

- Let the requester-initiator disconnect the *ReadBlock* at each ADB. The maximum sequence length for the *ReadBlock* transfers should be 321 bytes.

- Use sequence tag #30 for the I/O write transfer.

- Apply the I/O and ReadBlock addresses 3 clocks before asserting FRAME#.

#### Implementation /\* Program the behavior of the block transfers \*/

BX\_TRY(BestXRIGenDefaultSet(handle); BX TRY(BestXRIGenSet(handle, BX RIGEN NUMBEH, 5));

/\* Program the behavior properties steps, bytecount, and disconnect to behavior memory line 0 \*/

```

BX_TRY(BestXRIBehDefaultSet(handle, 0));

BX_TRY(BestXRIBehSet(handle, 0, BX_RIBEH_STEPS, 3));

BX_TRY(BestXRIBehSet(handle, 0, BX_RIBEH_BYTECOUNT, 321));

BX_TRY(BestXRIBehSet(handle, 0, BX_RIBEH_DISCONNECT, 1));

```

/\* Program the behavior properties steps, by tecount, and disconnect to behavior memory line 1 \*/

```

BX_TRY(BestXRIBehDefaultSet(handle, 1));

BX_TRY(BestXRIBehSet(handle, 1, BX_RIBEH_STEPS, 3));

BX_TRY(BestXRIBehSet(handle, 1, BX_RIBEH_BYTECOUNT, 321));

BX_TRY(BestXRIBehSet(handle, 1, BX_RIBEH_DISCONNECT, 1));

```

/\* Program the behavior properties steps and the tag to behavior memory line 2 \*/

BX\_TRY(BestXRIBehDefaultSet(handle, 2)); BX\_TRY(BestXRIBehSet(handle, 2, BX\_RIBEH\_STEPS, 3)); BX\_TRY(BestXRIBehSet(handle, 2, BX\_RIBEH\_TAG, 30)); /\* Program the behavior properties steps and the tag to behavior memory line 3 \*/

BX\_TRY(BestXRIBehDefaultSet(handle, 3)); BX\_TRY(BestXRIBehSet(handle, 3, BX\_RIBEH\_STEPS, 3)); BX\_TRY(BestXRIBehSet(handle, 3, BX\_RIBEH\_TAG, 30));

/\* Program the behavior properties steps and the tag to behavior memory line 4  $\ast/$

BX\_TRY(BestXRIBehDefaultSet(handle, 4)); BX\_TRY(BestXRIBehSet(handle, 4, BX\_RIBEH\_STEPS, 3)); BX\_TRY(BestXRIBehSet(handle, 4, BX\_RIBEH\_TAG, 30));

/\* Program the behaviors to the testcard's exerciser and run the exerciser. \*/

BX\_TRY(BestXExerciserProg(handle)); BX\_TRY(BestXExerciserRun(handle));

### Programming the Exerciser as a Completer-Target Device

A PCI-X completer-target device is the target of a transaction. It decodes all PCI-X bus transactions except split completion transactions.

To program the exerciser so that it acts as a PCI-X completer-target device, you have to:

• Set up the target decoders provided by the testcard for I/O, memory and configuration cycles.

See "Programming a Target Decoder" on page 41.

Because the decoders are closely linked to entries in the configuration space, you can program the decoders' base address, size and prefetch also by modifying the configuration space header. See *"Programming the Configuration Space"* on page 45.

**NOTE** The option to completely program the configuration space header is provided for very sophisticated tests, for example, to test systems without a BIOS or with a very rudimentary BIOS.

• Define how the completer-target reacts to transactions driven onto the bus.

See "Programming the Completer-Target Behavior" on page 48.

- Define how many behaviors are used before the first one is used again. See "Programming Generic Completer-Target Properties" on page 52.

- Specify the internal data resources.

See "Programming the Data Memory" on page 81 and "Programming the Data Generator" on page 73.

### **Programming a Target Decoder**

The completer-target needs the address range information to decide whether it has to react to transactions driven onto the bus. There are different types of decoders for different types of accesses (I/O, memory, configuration cycles).

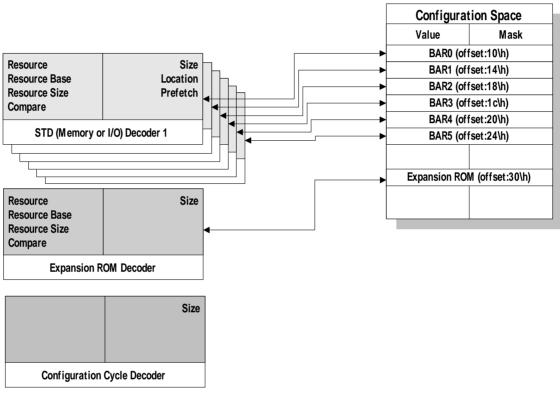

**Types of Decoders** The testcard provides the following target decoders:

- Three programmable memory decoders (six bars) for memory or I/O accesses (BX\_DEC\_BAR0 ... BX\_DEC\_BAR5)

These decoders are programmable regarding size, location, prefetch, compare and resource.

- Expansion ROM Decoder (BX\_DEC\_EXPROM) This decoder is programmable regarding size and resource (flash).

- Configuration Decoder (BX\_DEC\_CONFIG)

This decoder is only programmable regarding size (on/off) and reacts on PCI-X and PCI accesses.

**NOTE** The decoders are closely linked to entries in the configuration space. See the following figure.

Decoders Linked to the ConfigurationThe following figure shows the different decoders, the respective entriesSpace Headerin the configuration space header and how both can be programmed.

For programming the configuration space header, see "*Programming the Configuration Space*" on page 45.

Best XTDecoder Set/Get

Best XConf RegSet/Get Best XConf RegMaskSet/Get

Standard and expansion ROM decoders are equipped with a set of parameters that define their properties, such as whether the decoded memory space is prefetchable, or which data resource they are connected to. The configuration cycle decoder is only programmable regarding its size.

### How to Program a Decoder

To program a decoder:

- 1 Set all target decoder properties on the host to default values. Use *BestXTDecoderDefaultSet*.

- **2** To set the properties for the target decoder on the host, you can:

- Set all properties for a BAR decoder (BAR 0 ... 5) with *BestXTDecoderAllSet*.

- Set one property for one decoder (BAR 0 ... 5, EXPROM and configuration decoder) with *BestXTDecoderSet*.

To get a property value, use *BestXTDecoderGet*.

Dependencies between decoder and their programmable properties are shown in the following tables.

**Programmable Properties**

Which properties can be programmed for which decoder is shown in the following table:

| Decoder(s) | Property         | Value(s)                                       |

|------------|------------------|------------------------------------------------|

| Standard   | BX_DECP_SIZE     | Memory: 0, 2 63                                |

| EXPROM     |                  | I/0: 0, 2 31                                   |

| CONFIG     |                  | ExpROM: 0, 11 24                               |

|            |                  | Config: 0, 1                                   |

| Standard   | BX_DECP_LOCATION | BX_DECP_LOCATION_MEM<br>BX_DECP_LOCATION_IO    |

| Standard   | BX_DECP_PREFETCH | 0, 1                                           |

| Standard   | BX_DECP_RESOURCE | BX_DECP_RESOURCE_MEM                           |

| EXPROM     |                  | BX_DECP_RESOURCE_GEN<br>BX_DECP_RESOURCE_FLASH |

| Standard   | BX_DECP_RESBASE  | 0 224 in steps of 4                            |

| EXPROM     |                  |                                                |

| Standard   | BX_DECP_RESSIZE  | 2 24                                           |

| EXPROM     |                  |                                                |

| Standard   | BX_DECP_COMPARE  | 0, 1                                           |

Depending on the selected resource (BX\_DECP\_RESOURCE), programming the behavior of the completer-target is restricted. See the following table.

**Programmable Behaviors**

The following table shows the dependencies between resource and behavior.

| Resource          | Decoder(s) | Behavior                                                                |

|-------------------|------------|-------------------------------------------------------------------------|

| Memory, Generator | Standard   | Programmable                                                            |

|                   | EXPROM     |                                                                         |

| Flash             | EXPROM     | Fixed,<br>retries until data available,<br>single data phase disconnect |

| Config space      | CONFIG     | Fixed                                                                   |

**3** Write the properties to the testcard with *BestXExerciserProg*.

### **Example for Programming a Decoder**

**Task** Set up a standard decoder with the following properties:

- Decoder size 12, Memory, Prefetch

- Resource: Date memory, resource size 12, internal resource base address 0

- Base Address: 0x10003000

# Implementation /\* Setup the memory decoder (baseaddress = 10003000\h, size=c\h) \*/

```

bx_int32 dsize=0xcUL;

bx_int32 bbase=0x10003000UL;

BX_TRY(BestXTDecoderDefaultSet(handle));

BX_TRY(BestXTDecoderSet(handle, BX_DEC_BAR0, BX_DECP_LOCATION,

BX_DECP_LOCATION_MEM));

BX_TRY(BestXTDecoderSet(handle, BX_DEC_BAR0, BX_DECP_SIZE, dsize));

BX_TRY(BestXTDecoderSet(handle, BX_DEC_BAR0, BX_DECP_PREFETCH, 1));

BX_TRY(BestXTDecoderSet(handle, BX_DEC_BAR0, BX_DECP_RESOURCE,

BX_DECP_RESOURCE_MEM));

BX_TRY(BestXTDecoderSet(handle, BX_DEC_BAR0, BX_DECP_RESBASE,

0x0));

BX_TRY(BestXTDecoderSet(handle, BX_DEC_BAR0, BX_DECP_RESSIZE,

dsize));

```

### **Programming the Configuration Space**

You can program every single register of the testcard's configuration space header.

Usually, all settings in the configuration space header that need to be made when starting the system are either made by the BIOS or by programming target decoders. The latter applies to settings concerning the base address registers.

**NOTE** The option to completely program the configuration space header is provided for very sophisticated tests, for example, to test systems without a BIOS or with a very rudimentary BIOS.

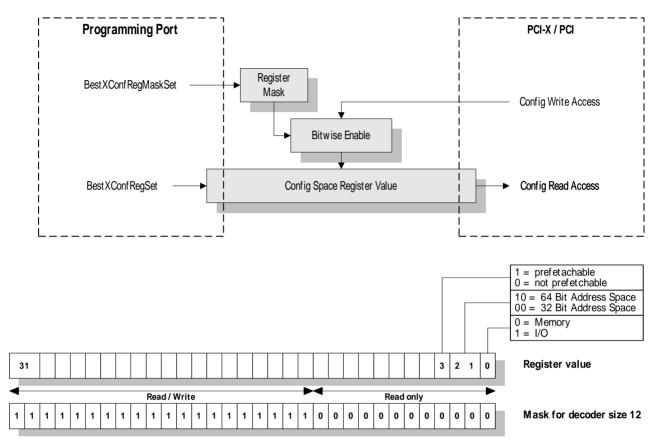

For every bit of the various registers in the configuration space header, you can determine whether it is fixed (read-only) or programmable from outside (BIOS) (read/writeable). For both types, values can be specified as required for BIOS configuration during system startup:

- Determine **read-only** values, for example, a "Vendor ID", which can then be evaluated by the BIOS.

- Determine **read/writeable** values, for example, base address register entries. They can be used by the BIOS to determine the wanted size of the decoded address range and will then be overwritten with the actual base address.

### How to Modify the Configuration Space

To modify the configuration space header:

- **1** Set the register value and the register mask that configures the status of a bit within a register on the host.

- To set a register mask, use *BestXConfRegMaskSet*.

In the 32-bit mask:

- 0 means: This bit is fixed (read-only) and its value cannot be changed.

- 1 means: This bit is programmable.

- To set the value of a register, use *BestXConfRegSet*.

#### CAUTION

Do not set several address spaces to the same decoding location, because the system under test can crash or could even be damaged. The following figure shows the dependencies for accessing the configuration space between the programming port (C-API) and the PCI-X/PCI interface (BIOS).

**2** Write the values to the testcard with *BestXExerciserProg*.

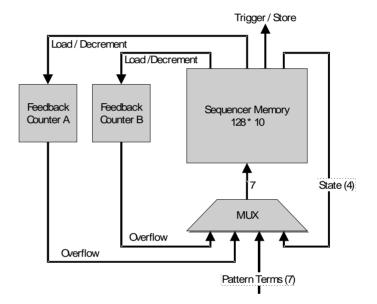

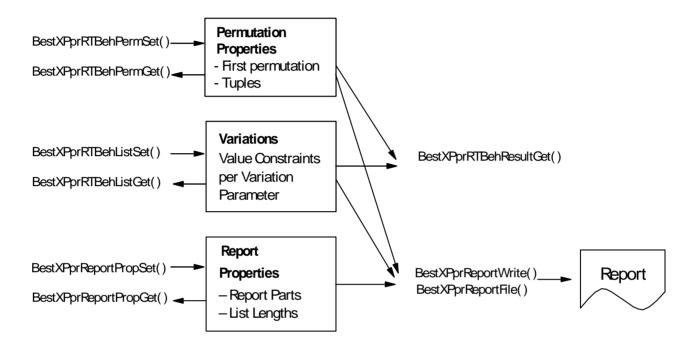

### **Example for Modifying the Configuration Space**